### Optical Proximity Communication for a Silicon Photonic Macrochip

John E. Cunningham, Ivan Shubin, Xuezhe Zheng, Jon Lexau, Ron Ho, Ying Luo, Guoliang Li, Hiren Thacker, J. Yao, K. Raj and Ashok V. Krishnamoorthy

Sun Microsystems, CTO, Physical Science Center San Diego, CA 92121, USA john.cunningham@sun.com

Mehdi Asghari, Dazeng Feng, Jonathan Luff, Hong Liang and Cheng-Chih Kung Kotura Inc., 2630 Corporate Place, Monterey Park, CA 91754, USA

"This research was, in part, funded by the U.S. Government. The views and conclusions contained in this document are those of the authors and should not be interpreted as representing the official policies, either expressed or implied, of the U.S. Government."

# Outline

- Background and motivation

- Macrochip

- Optical proximity communication

- Packaging with new chip alignment technology

- WDM point-to-point network for multi-chip interconnects

- Device requirements and consideration

- Summary

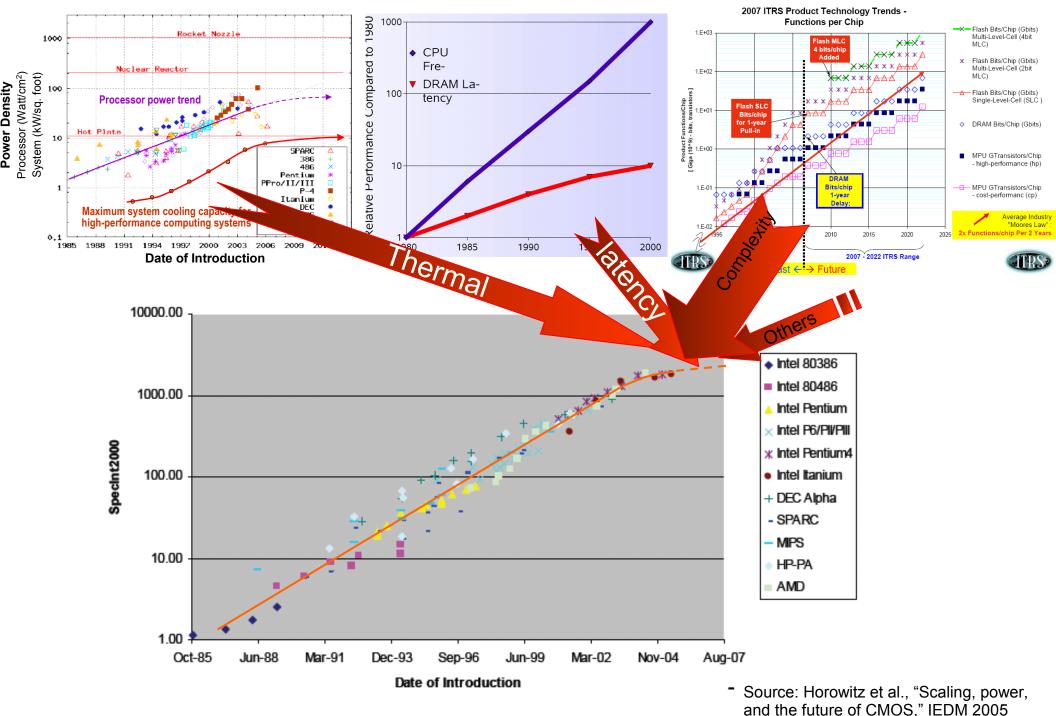

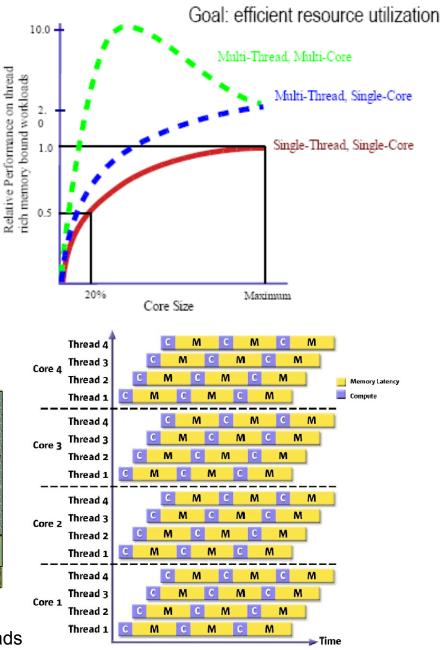

#### Moore's law is leveling off for single core processors...

### Continuing Moore's Law scaling

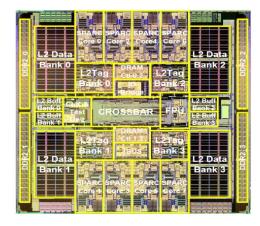

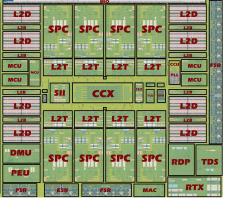

- Multi-core and CMT

- > CMT = chip multi-threading

- Efficiently use chip area

- > But chip real estate is precious

- > Multicore die at the reticle limit

S. Manish et al., ASSCC '07. IEEE Asian 12-14 Nov. 2007

Niagara 2: 8 cores, 64 threads

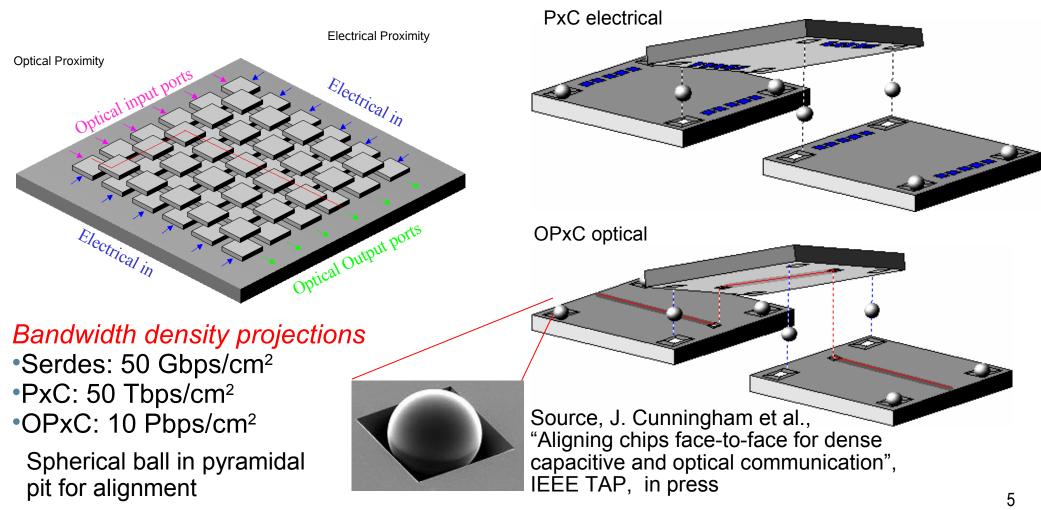

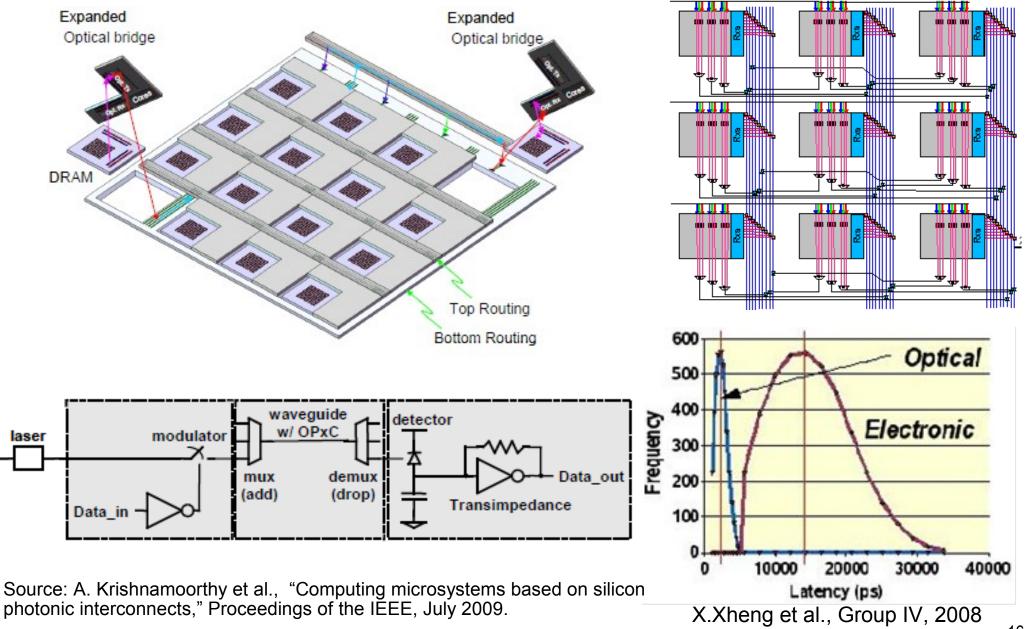

# Multichip arrays with optical routing "Macrochip": a logical big die made of small chips

- Breaks the reticle limit to provide enormous Si real estate

- Transparent optical routing fabrics Enabled by optical proximity communication (OPxC)

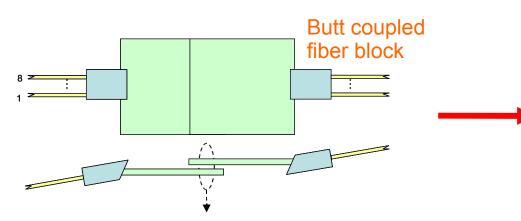

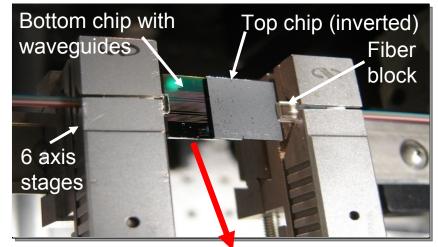

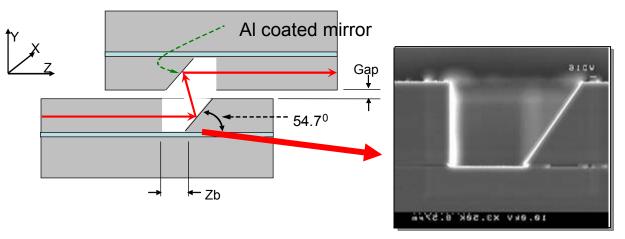

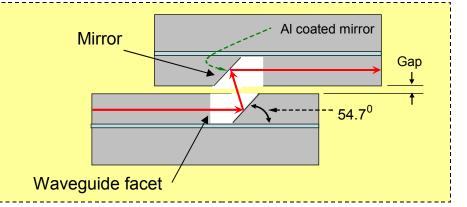

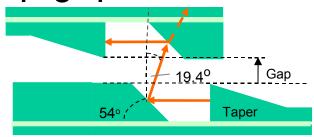

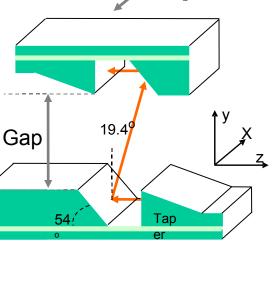

### Experimental setup: face-to-face chips

X. Zheng et.al. , Optics Express ,2008

### Coupling losses: today vs target

| Source of loss  | Losses (dB) per chip* |        | Natas                                                        |

|-----------------|-----------------------|--------|--------------------------------------------------------------|

|                 | Now                   | Target | Notes                                                        |

| Mirror          | 0.3                   | 0.2    | Metal reflectivity, thin film and roughness improvement      |

| Waveguide facet | 0.3                   | 0.25   | Roughness facet angle and ARC improvement                    |

| Mode mismatch   | 0.15                  | 0.15   | Asymmetric modes, one upside down with respect to the other  |

| Beam divergence | 0.75                  | 0.2    | Current cavity length is ~66um target<br>to go down to <30um |

| Total           | 1.5                   | 0.8    |                                                              |

\* Alignment tolerances not included

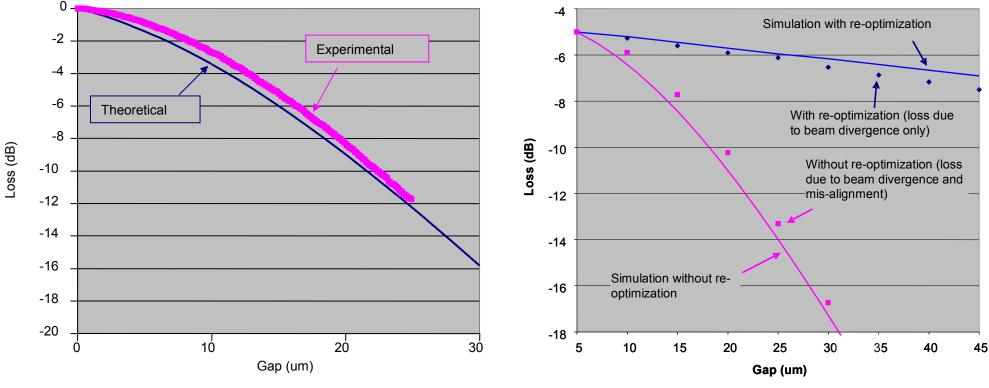

# Vertical misalignment tolerance

- Insertion loss increases with chip-to-chip gap

- Depolarized, broadband light source

Data normalized to loss at min gap

**Un-optimized**

**Re-optimized**

A. Krishnamoorthy et.al., JQE, 2009

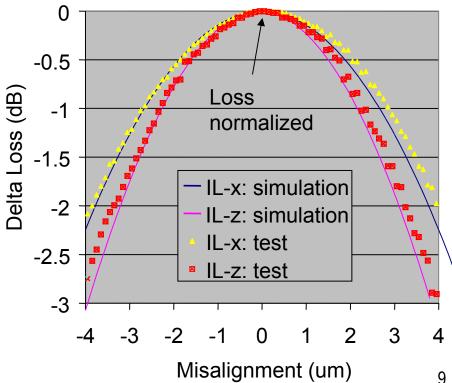

## In-plane misalignment tolerance

- Scan chip positions

In lateral (in-plane) directions

- Monitor change in the coupling loss

- Results shown at the right, along with simulation

- Simulations assume depolarized broadband light

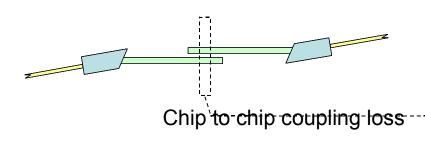

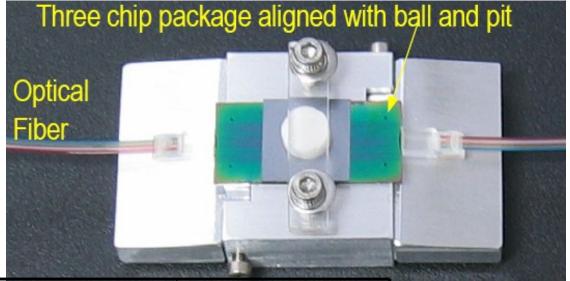

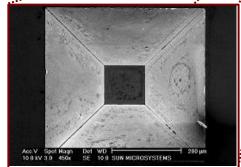

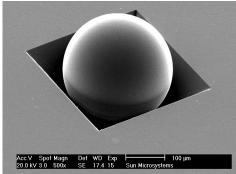

# OPxC in a package

- Three aligned chips

- > Balls in pyramidal pits

- Optical losses 4.0dB

- > 1 dB more than w/ 6-axis aligner & single OPxC hop

J. Cunningham et.al. Group IV, 2008

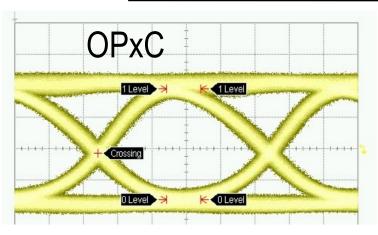

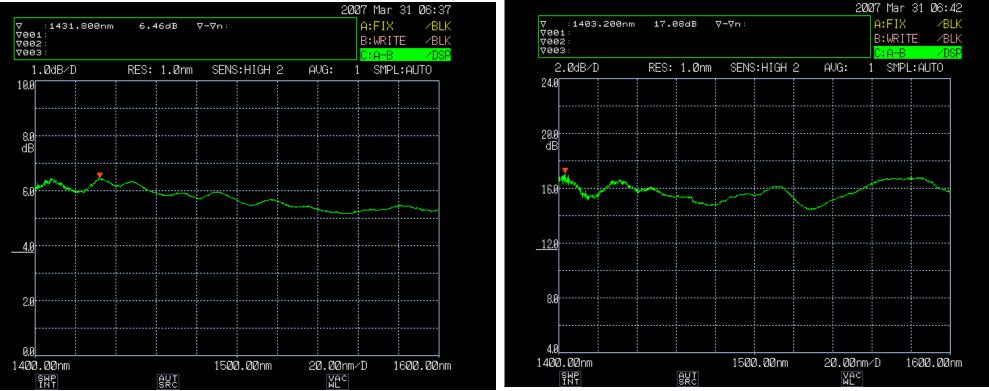

| Metric at 10Gbps     | Back to back | With OPxC hop |

|----------------------|--------------|---------------|

| Q ( signal to noise) | 10.44        | 10.33         |

| RMS jitter           | 2.62 ps      | 2.62 ps       |

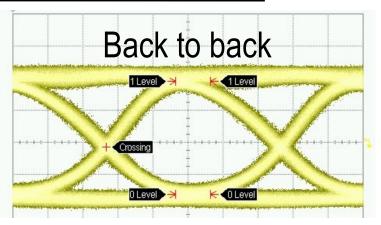

## Broadband wavelength coupling

- Spectral characteristics of OPxC

- Transmission versus wavelength

- Wavelength Division Multiplexing possible

One OPxC hop

Two OPxC hops

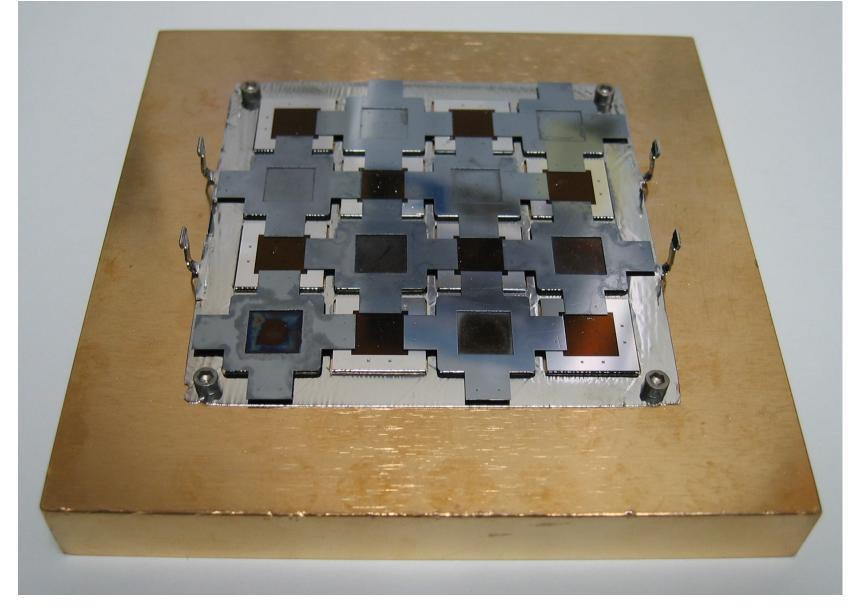

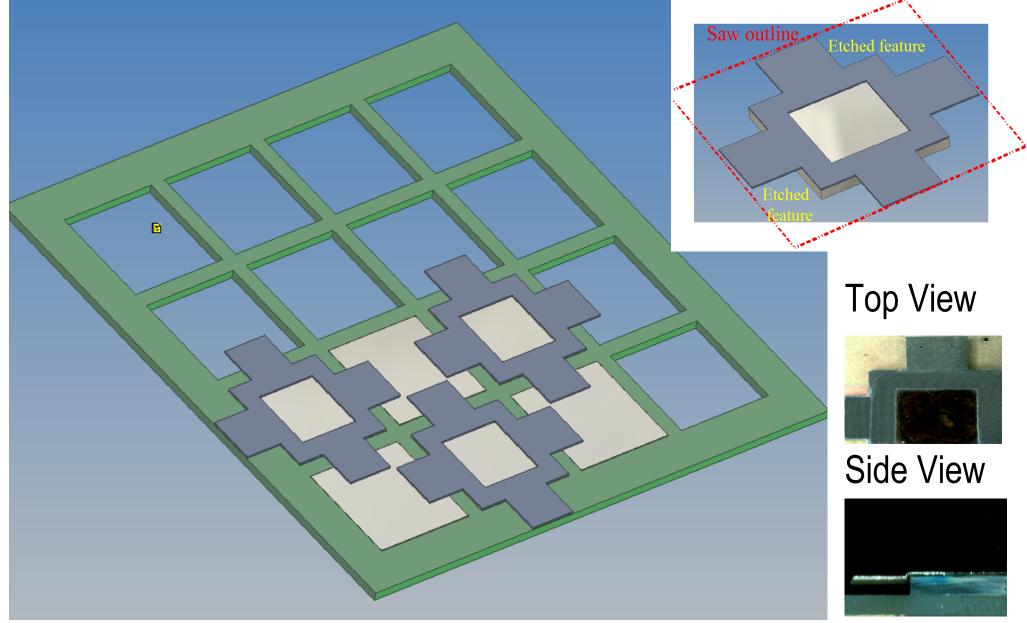

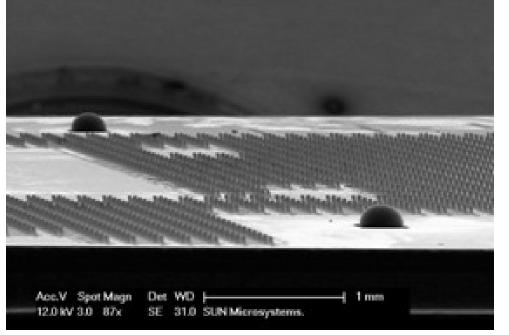

### 4x4 with $1\mu m$ global positioning using ball and pit

J. Cunningham et al. "Coupled Data Communications", R. Ho and R. Drost, eds., Springer-Verlag, in press

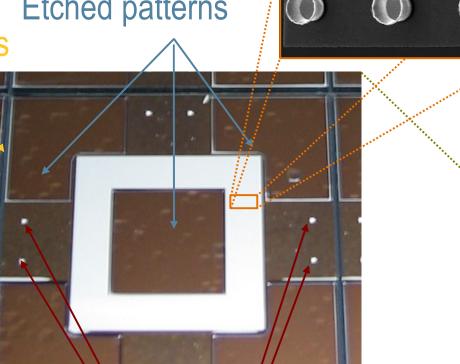

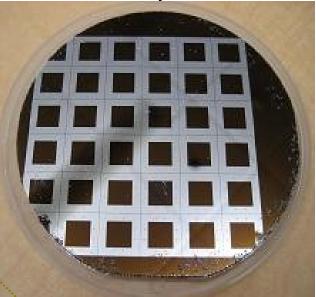

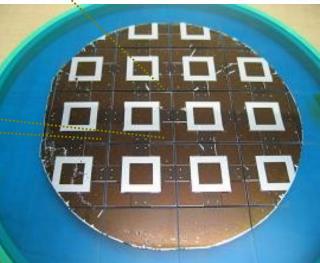

#### Wafer-scale Fab micro-bumps

#### **Etched** patterns Saw lanes

Etch pits

### **Island Chip Wafer**

### Sombrero Bridge Wafer

Source, J. Cunningham et al., "Aligning chips face-to-face for dense capacitive and optical communication",IEEE TAP in press

### **Chip Lattice for Coarse Alignment**

### **Remateable Power and Ground: the KGD-MCM problem**

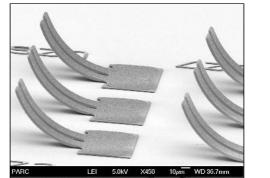

### PARC Technology

Sacrificial layer etch, spring lift-off and Au-plating

SEM image. Micro-spring interconnects

### SUN Technology

#### Package to test rematability

#### I. Shubin et al., ECTC 2009

### **Macrochip with SiPhotonics**

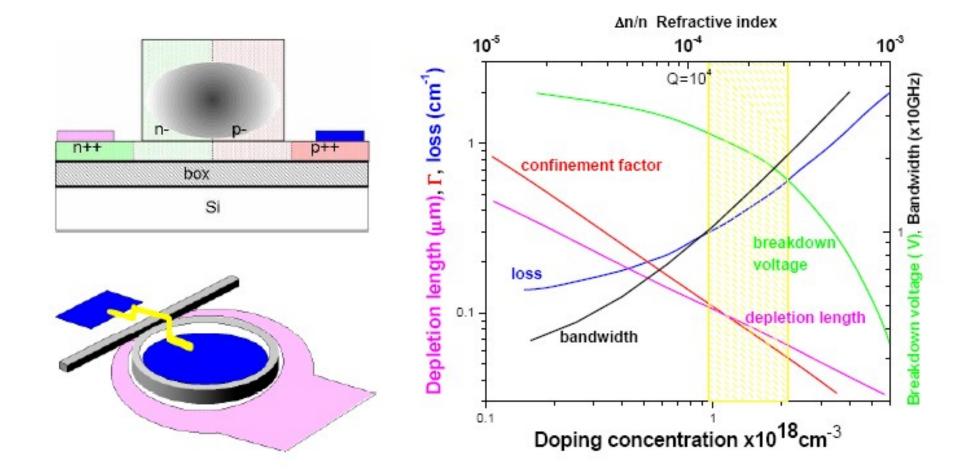

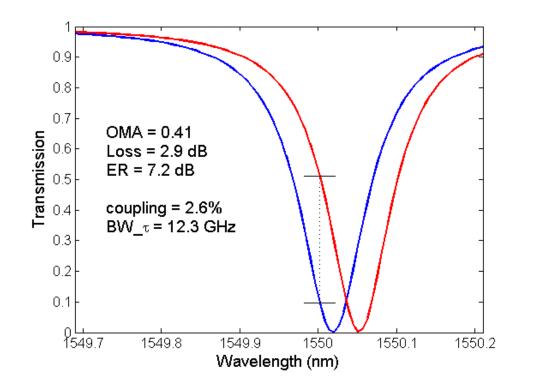

# Device considerations modulators Design space for fast ring modulators

# **Ring Modulator Analysis**

Expected performance with 2V swing in reverse bias

Modulation> 7 dB Insertion loss <3dB

Use 30 um ring diameter, 60% modulation length. Doping density 1e18.

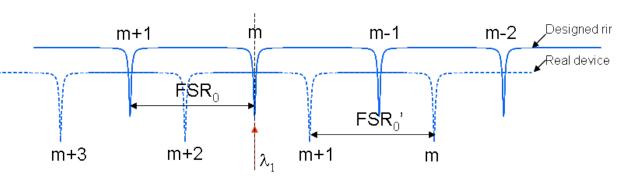

# **Tuning for WDM devices**

- Energy per bit to communicate

- Lots of modulation progress: 1/4 CV<sup>2</sup> down to < 100 fJ/bit</li>

- Challenge to tune ring modulators onto ITU grid

- Tuning with forward bias degrades resonantor's Q

- Large thermal energy per bit penalty to tune

- Large error in resonance due to microfab variation

Source: A. Krishnamoorthy et al., "Computing microsystems based on silicon photonic interconnects," Proceedings of the IEEE, July 2009.

### Summary

- Break the single "reticle" limit for performance

- Integrate many chips as a logical large "macrochip"

- > Optically interconnected macrochip enabled by Si photonics

- Key enabling technology OPxC demonstrated with promising performance and potential packaging solutions

- WDM point-to-point network for macrochip

- > Highly transparent, seamless network w low and uniform latency

- > High sustainable bisection bandwidth insensitive to message size

- New Optical devices

- > Lower energy per bit, smaller footprint

- > Stronger electro-optic effect

- Low Power Devices necessary

- > Roadmap to 300fJ/bit

- > Low power transmitter demonstrated

(X. Zheng et at., "Ultra-Low Power All CMOS Si Photonic Transmitter," OSA Frontiers in Optics, 2009 R. Ho et al., "Circuits for silicon photonics on a 'macrochip," IEEE ASSCC, in press, November 2009.)

### Thank you!

• This material is based upon work supported, in part, by DARPA under Agreement No. HR0011-08-09-0001.