# **Hybrid Optoelectronic Router**

Ryohei Urata,

Tatsushi Nakahara, Hirokazu Takenouchi, Toru Segawa, Ryo Takahashi

NTT Photonics Laboratories, NTT Corporation

Supported in part by the National Institute of Information and Communications Technology (NICT)

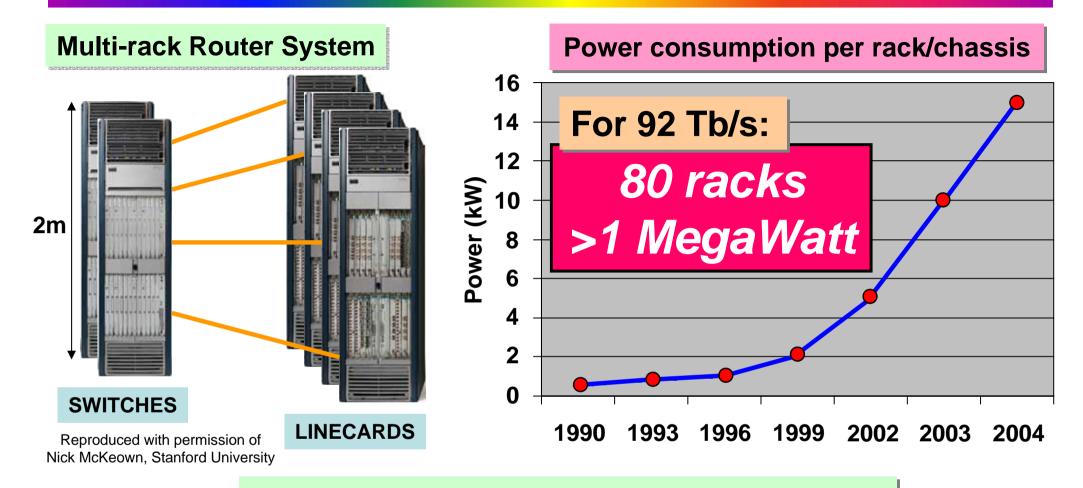

### **Electrical Routers**

Need to...

- Reduce power consumption

- > Reduce size

- > Increase performance

- Increase throughput

- Increase traffic engineering capability

### **Problem with Electrical Routers**

- > Excessive buffering and processing

- > Problems at the interfaces (MUX/DEMUX)

- High power consumption

- Speed limited by electronic components

### **Photonic Router**

**Electrical Router**

High Capacity

Compact

Low Power Low Latency

**Photonic Router**

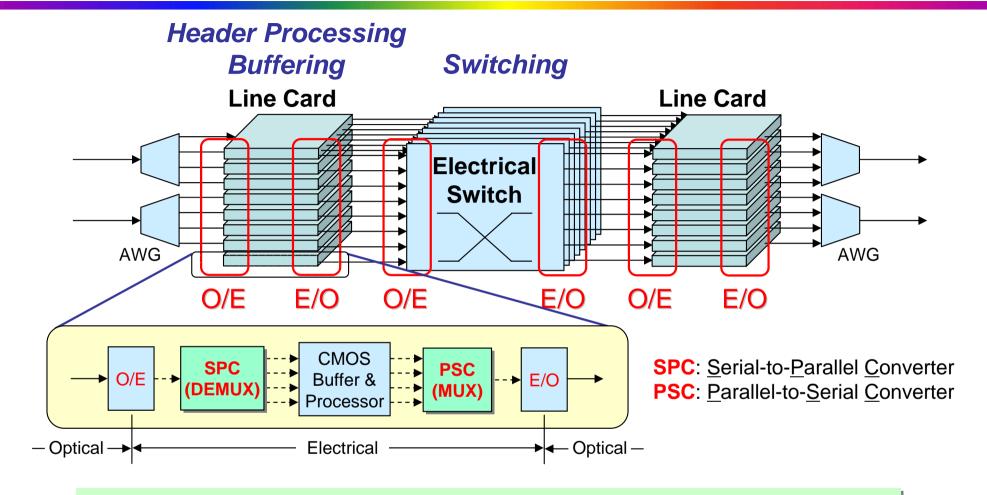

Buffering Label Proc. Switching

Novel optical device and subsystem stechnologies for processing burst packets

New router architecture incorporating optical technologies

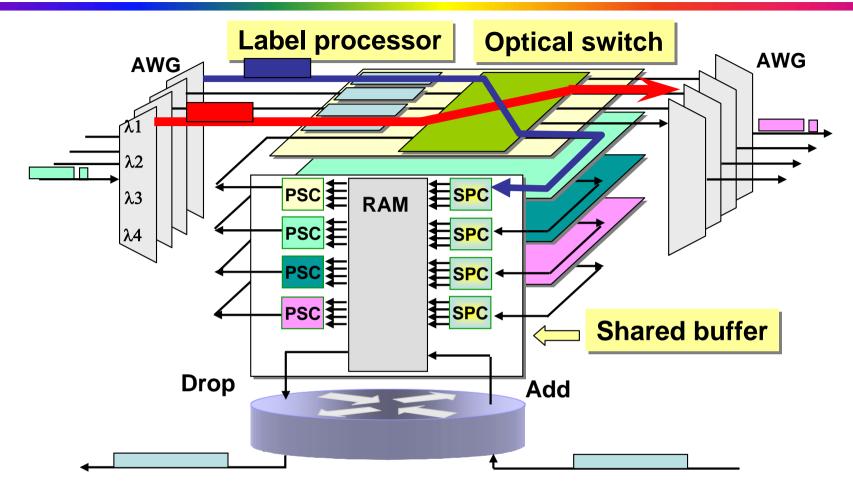

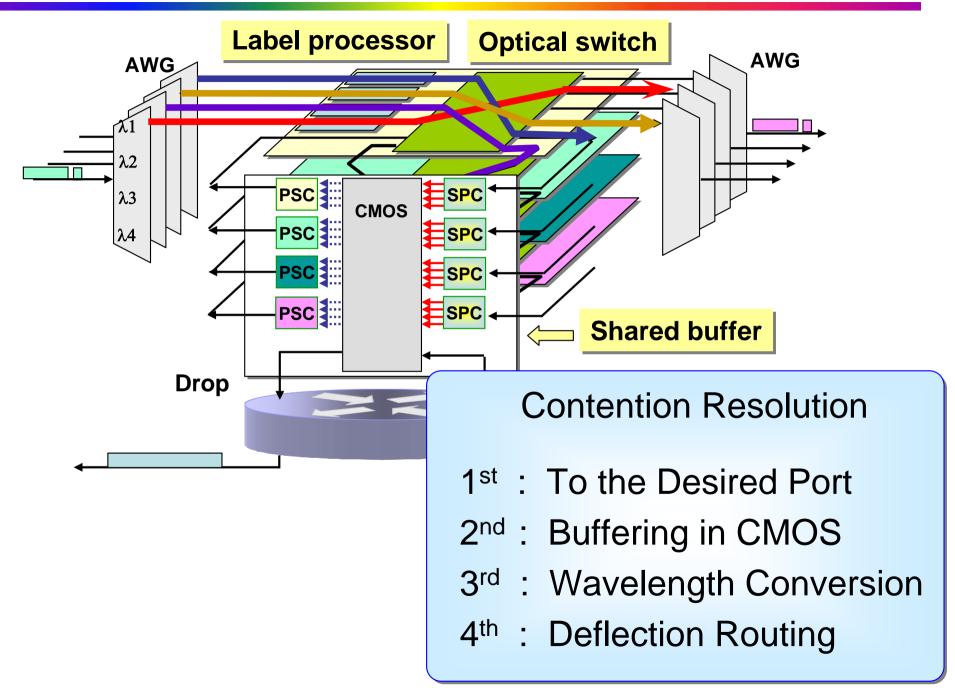

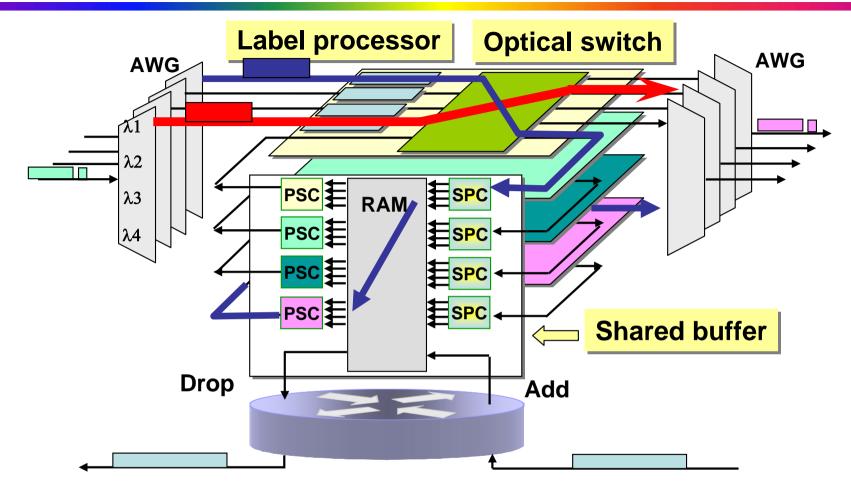

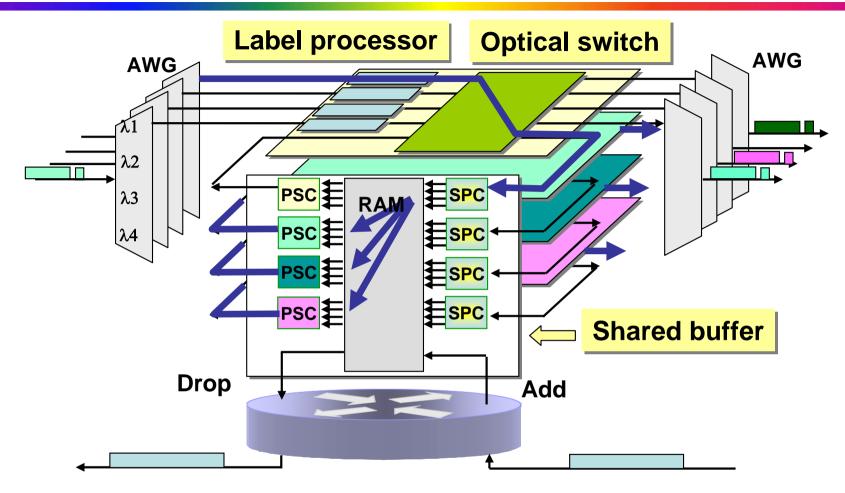

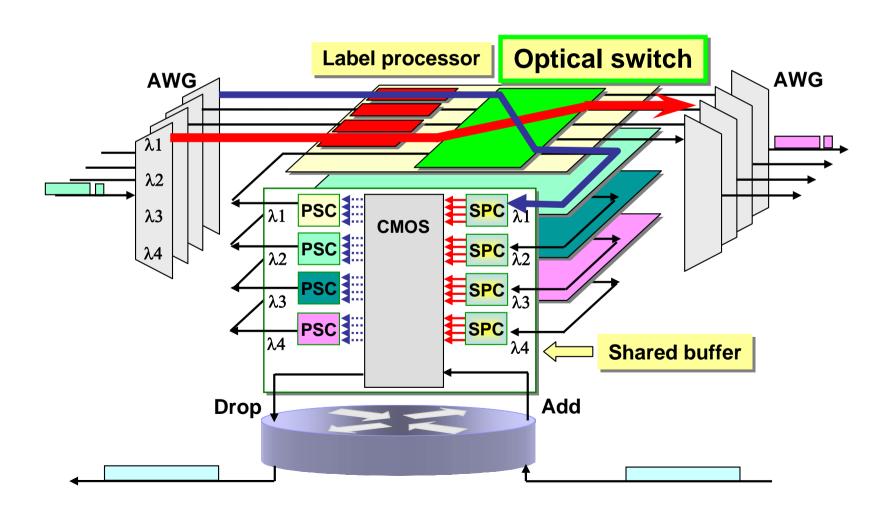

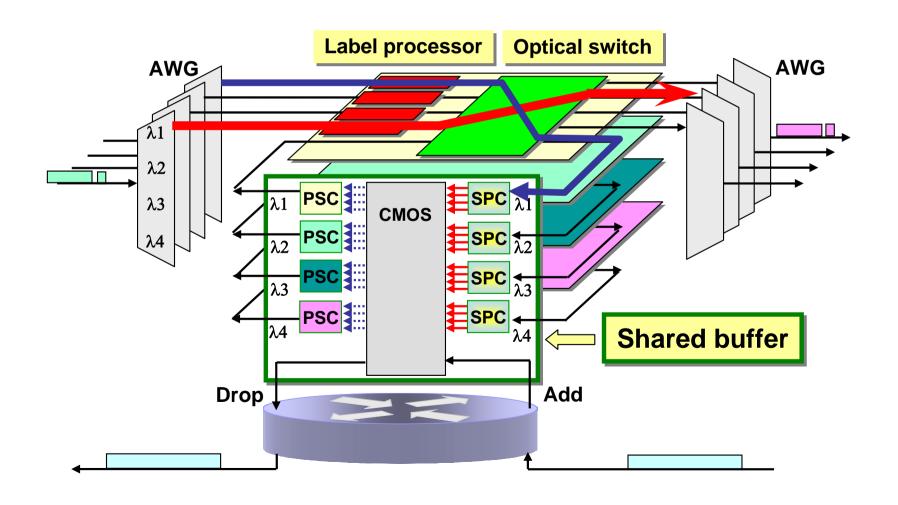

# Hybrid Optoelectronic Router Node Architecture

No contention

Passes through transparently

**Contention**

Forwarded to shared buffer

### **Buffering in CMOS RAM**

Traffic engineering between wavelength layers

3R regeneration based on TTL

**Buffer supports various services**

QoS, FEC, Multicast routing, Policy routing

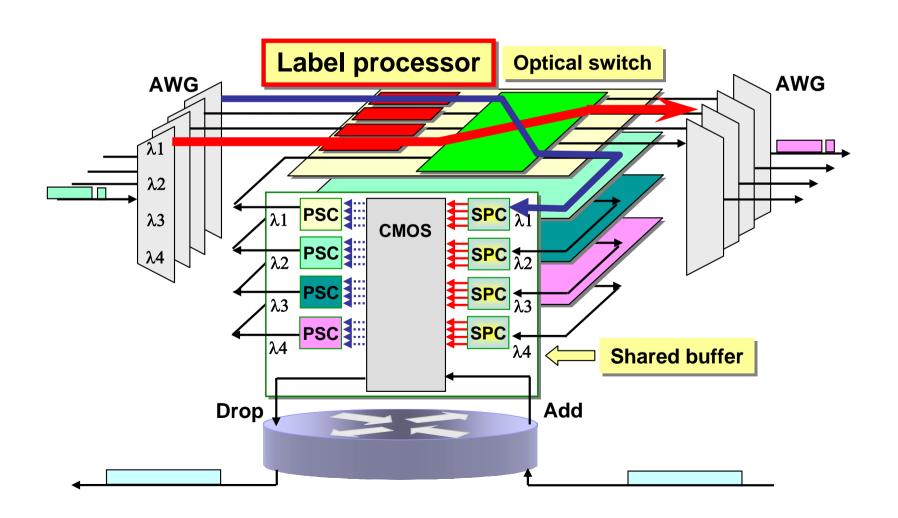

# **Sub-Systems**

# **Label Processor**

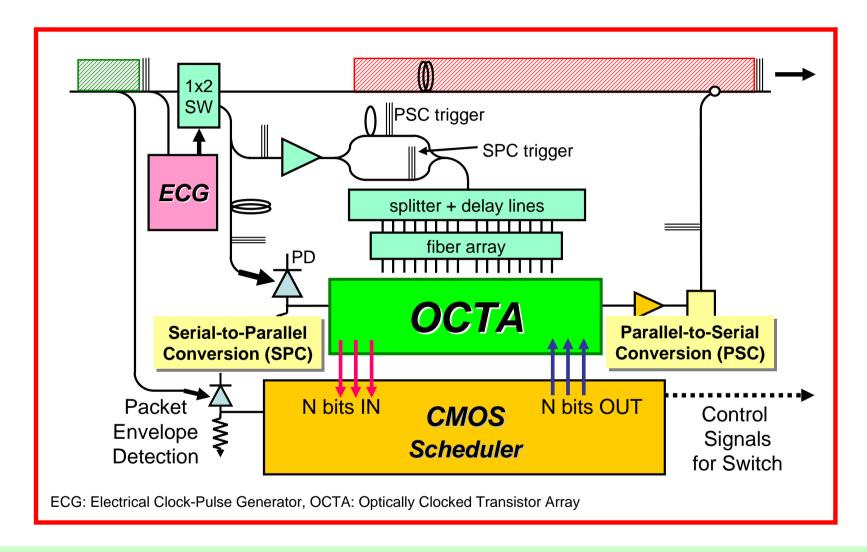

## **Label Processor Sub-System**

Detect input label, packet envelope Process label, configure switch

Merges SPC, PSC, clock generation for compact, low-power system

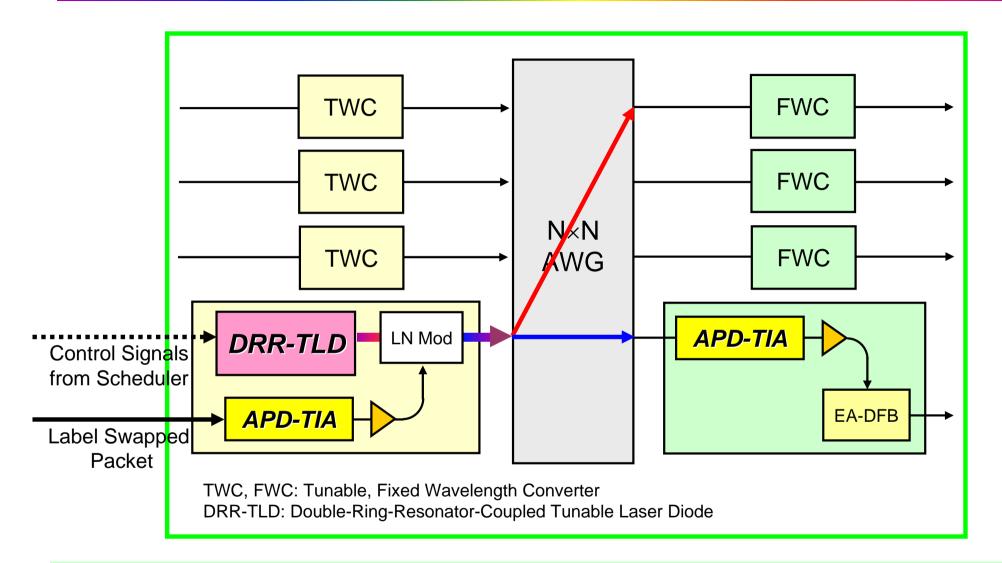

# **Optical Switch**

### **Optical Switch Sub-System**

N×N non-blocking switch for packet-level switching

Low power, compact, fast switching, scalable

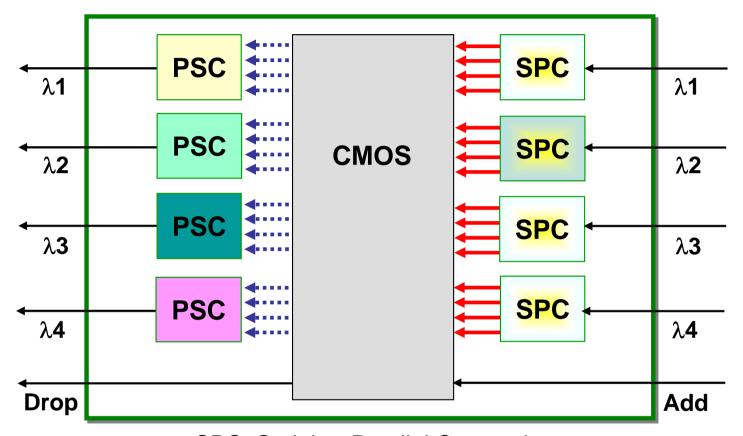

# **Shared Buffer**

### **Shared Buffer**

SPC: Serial-to-Parallel Conversion PSC: Parallel-to-Serial Conversion

#### Selective buffering, high-level packet functions

Asynchronous burst mode compliant, low power, CMOS functionality

### Conclusion

Optical Technology + Electrical Technology

- Optical technologies for high-speed burst packet processing

- Node architecture for transparency and high functionality

- Optically Clocked Transistor Array (OCTA)

- Double-Ring Resonator Tunable Laser

- All-Optical Serial-to-Parallel Converter (SPC)

- Optical Clock-Pulse-Train Generator (OCPTG)